12.02.2025, 03:51 PM

(Dieser Beitrag wurde zuletzt bearbeitet: 12.02.2025, 04:00 PM von Gucki.)

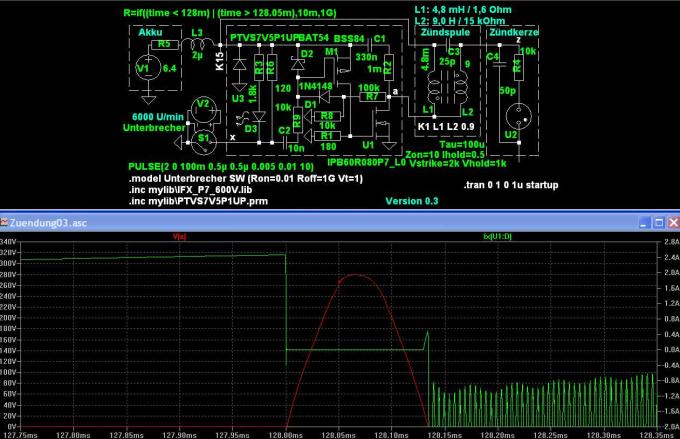

Nun ist endlich auch die SOA-Kontrolle gelungen.

Die Zündkerze hab ich unterbrochen. Und den C1-ESR hab ich auf 1 mOhm herabgesetzt.

Ich unterbreche den Akku bei 128ms. Die Spannung an C1 rast hoch. Genau bei 128.05 ms bzw. 270V bekommt der Akku wieder Kontakt und die Elektronik möchte den NMOS wieder einschalten.

Es würden also 330nF über 40mOhm entladen werden. Ein großer 6750A-Knall (*)

Man sieht jedoch, dass kein NMOS-Strom fließt, so lange die Drain-Spannung nicht in ungefährliche Bereiche gesunken ist. Dafür sorgt die erweiterte PMOS-Gatebeschaltung.

----------------

Mir gefällt die V0.2 mit dem 5.6 Ohm C1-ESR besser. In der geschilderten Situation würden dort 48A (*) fließen. Man muss nur darauf achten, dass der 5.6 Ohm-Widerstand diesen Spitzenstrom aushält, ohne zu verdampfen.

(*) Die Ströme werden in der V0.2 und V0.3 noch von dem Akkuinnenwiderstand und der Zuleitungsinduktivität gebremst (= "kahlos C1-Anordnung"). In den vorigen Schaltungen hier im Thread war C1 direkt parallel zum NMOS. Da gab es nur die ESR Bremse und sonst nichts.

Die Zündkerze hab ich unterbrochen. Und den C1-ESR hab ich auf 1 mOhm herabgesetzt.

Ich unterbreche den Akku bei 128ms. Die Spannung an C1 rast hoch. Genau bei 128.05 ms bzw. 270V bekommt der Akku wieder Kontakt und die Elektronik möchte den NMOS wieder einschalten.

Es würden also 330nF über 40mOhm entladen werden. Ein großer 6750A-Knall (*)

Man sieht jedoch, dass kein NMOS-Strom fließt, so lange die Drain-Spannung nicht in ungefährliche Bereiche gesunken ist. Dafür sorgt die erweiterte PMOS-Gatebeschaltung.

----------------

Mir gefällt die V0.2 mit dem 5.6 Ohm C1-ESR besser. In der geschilderten Situation würden dort 48A (*) fließen. Man muss nur darauf achten, dass der 5.6 Ohm-Widerstand diesen Spitzenstrom aushält, ohne zu verdampfen.

(*) Die Ströme werden in der V0.2 und V0.3 noch von dem Akkuinnenwiderstand und der Zuleitungsinduktivität gebremst (= "kahlos C1-Anordnung"). In den vorigen Schaltungen hier im Thread war C1 direkt parallel zum NMOS. Da gab es nur die ESR Bremse und sonst nichts.