11.05.2023, 04:32 PM

(Dieser Beitrag wurde zuletzt bearbeitet: 11.05.2023, 05:18 PM von christianw..)

R9 geändert von 68k auf 8k3

R1 geändert von 33k auf 4k22

R3 geändert von 10R auf 0R

C1 + C2 entfernt

scheint besser aber noch nicht optimal.

Hmm, ich habe testweise 220nF direkt an GS gelötet mit R3 = 22R - ohne zusätzliche Kapazität gibts einen "Glitsch" beim einschalten.

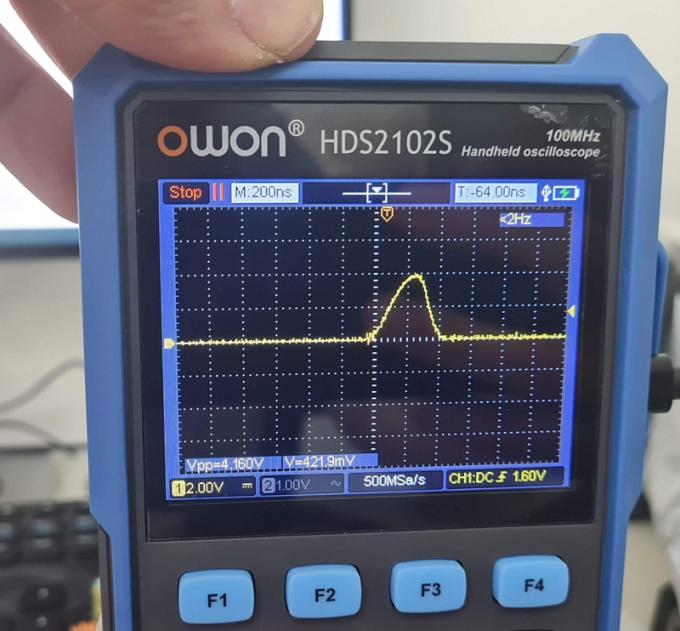

Bild zeigt Vgs von Q1, ist aber nicht relevant.

Die Spannung am Gate sinkt nach trennen der Quelle nicht schnell genug ab, so dass der FET durchaus noch eingeschaltet sein kann, wenn wieder zugeschaltet wird - damit fließt dann "voller" Strom.

R1 geändert von 33k auf 4k22

R3 geändert von 10R auf 0R

C1 + C2 entfernt

scheint besser aber noch nicht optimal.

Hmm, ich habe testweise 220nF direkt an GS gelötet mit R3 = 22R - ohne zusätzliche Kapazität gibts einen "Glitsch" beim einschalten.

Bild zeigt Vgs von Q1, ist aber nicht relevant.

Die Spannung am Gate sinkt nach trennen der Quelle nicht schnell genug ab, so dass der FET durchaus noch eingeschaltet sein kann, wenn wieder zugeschaltet wird - damit fließt dann "voller" Strom.