wobei...etwas gegrübelt...reizvoller wäre dann sowas:

- OC1A : macht PWM , 7bit , also OC1C auf 127 gesetzt;

- PLL im low-power-mode , macht dann 32MHz , somit der timer wieder 250kHz pwm .

- OC1B : bekommt auch 7bit Wert...und zwar so:

es wird ne Tabelle erzeugt, wenn genug Speicher in deinem mini-tiny hast, mit 512 x 16bit Werten (1kB, köönte gehen, sonst eben 256 Werte

);

die 16bits sind je 1Byte MSB mit 7bits maximum, und 1 LSB mit den restlichen 7 bits; (jeweils left-just.);

vom oc1a out kommt statt der Monster-Drossel ein R , zb 4k7 , zum VOL-poti; vom oc1b (4k7 x 128 = ) 602k auch , das ist das "LSB" ;

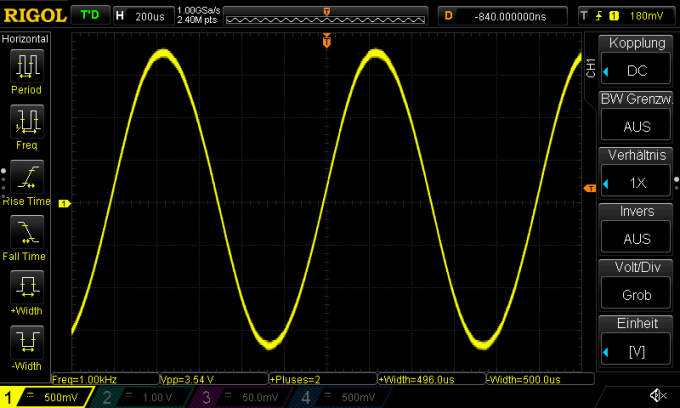

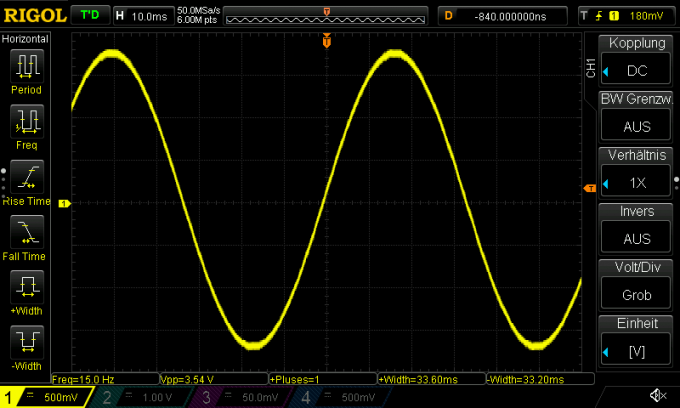

somit wirds eine 14-bit / 250kHz Auflösung, die theoretisch > 80dB S/N und 0,01% Klirr erreicht (dominanter Fehler sind da das matching des 1/128 R-verhältnisses und die Nichtlinearität der Portpins) und 0...20kHz problemlos macht.

in diesem etwas komplexeren Gewerkel muss allerdings etwas umverdrahtet werden: oc1b kommt auf PB4 raus, also müssen R22+28 raus, frequ.poti A/D in kommt auf PB3 ; somit pb4 frei, bekommt den 600k zum Vol-poti. + der 100n -> 2n2 , wir machen jetzt ja 20kHz. max.

software - das timer-update lädt dann eben zwei aufeinanderfolgende Bytes, in oc1a und oc1b ; minimaler Mehraufwand.

cool wa ?

ps pb3 sollte wohl die betriebsspannung messen..oder wie? geht auch so: du misst die interne Referenz , 1.1V : was da gemessen wird.../Milchmädchenrechnung/...ergibt die VCC .

.

.