09.07.2018, 03:46 PM

(Dieser Beitrag wurde zuletzt bearbeitet: 09.07.2018, 03:47 PM von christianw..)

Das Problem liess sich lösen.

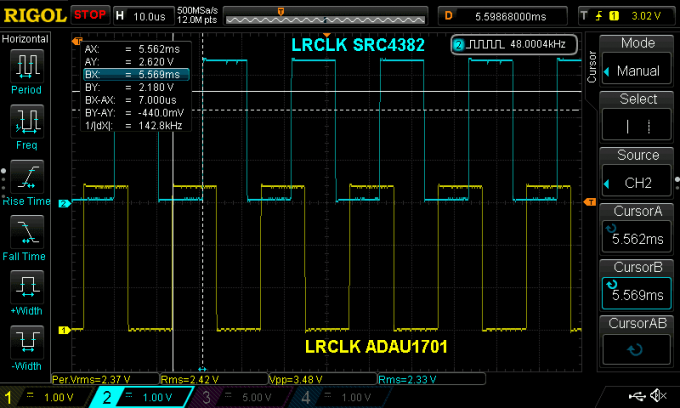

In Gelb der LRCLK vom ADAU1701 an seinem Ausgang, in türkis der LRCLK am Ausgang des SRC4382 PortA. Bedingt durch die Beschaltung auf meiner Platine treibt PortA des ADAU mit LRCLK und BCLK, LRCLK und BCLK für seinen Ausgang erzeugt er selbst. Da daran normal nur ein PCM5102 hängt, ist das egal.

Wenn man nun allerdings I2S vom CSR64215 einspeist, ergibt sich durch die vorliegende Pinkonfiguration ein Problem durch den im Bild dargestellten Offset.

LRCLK und BCLK bekommt der CSR64215 vom ADAU1701 Ausgang womit er seine SDATA darauf synchroniert. Da der ADAU1701 BCLK und LRCLK vom SRC4382 bekommt funktioniert die Synchronisation nicht. (logisch) Dadurch ergaben sich diese Effekte, dass es mit RJustified irgendwie ging (manchmal).

Ich habe jetzt Ein- und Ausgänge gepatcht, so dass der SRC4382 am PortA ebenfalls als Slave läuft. Warum der SRC diesen Offset produziert ist nicht klar, aber wahrscheinlich seiner PLL geschuldet. MCLK passt natürlich immer, logisch.

Nun funktioniert auch alles wie es soll mit den Einstellungen wie am Sure DSP. Max Pegel vom CSR komment ist -3dB.

In Gelb der LRCLK vom ADAU1701 an seinem Ausgang, in türkis der LRCLK am Ausgang des SRC4382 PortA. Bedingt durch die Beschaltung auf meiner Platine treibt PortA des ADAU mit LRCLK und BCLK, LRCLK und BCLK für seinen Ausgang erzeugt er selbst. Da daran normal nur ein PCM5102 hängt, ist das egal.

Wenn man nun allerdings I2S vom CSR64215 einspeist, ergibt sich durch die vorliegende Pinkonfiguration ein Problem durch den im Bild dargestellten Offset.

LRCLK und BCLK bekommt der CSR64215 vom ADAU1701 Ausgang womit er seine SDATA darauf synchroniert. Da der ADAU1701 BCLK und LRCLK vom SRC4382 bekommt funktioniert die Synchronisation nicht. (logisch) Dadurch ergaben sich diese Effekte, dass es mit RJustified irgendwie ging (manchmal).

Ich habe jetzt Ein- und Ausgänge gepatcht, so dass der SRC4382 am PortA ebenfalls als Slave läuft. Warum der SRC diesen Offset produziert ist nicht klar, aber wahrscheinlich seiner PLL geschuldet. MCLK passt natürlich immer, logisch.

Nun funktioniert auch alles wie es soll mit den Einstellungen wie am Sure DSP. Max Pegel vom CSR komment ist -3dB.